# IM6102 Memory Extension/ DMA Controller/ Interval Timer (MEDIC)

### **FEATURES**

- Provides Extended Memory Address to 32K Words

- Simultaneous DMA Provides Simultaneous DMA Channel that Uses DX Bus During Second Half of a Cycle to Access Memory

- DMA Channel Can be Used for Dynamic RAM Refresh

- 12-Bit Programmable Interval Timer

- Direct Interface with IM6100 Microprocessor Via Bidirectional DX Bus and Handshake Lines

- Hardware Reset

- 28 Different I/O Instructions

#### **GENERAL DESCRIPTION**

The IM6102 is a multi-function peripheral controller chip incorporating functions such as memory extension, direct memory access control, and a programmable real time clock.

The IM6102 provides necessary control to address up to 32K words of memory, and its DMA channel can be used with Dynamic RAM Components for "transparent refresh". The programmable real time clock is 12-bit long, and its output frequency can be programmed for 5 decades.

It features a high degree of system integration, putting into one chip all the functions which are normally available in three or more LSI circuits. As a result of this large integration, the user can design and produce a compact microcomputer with minicomputer performance.

# ABSOLUTE MAXIMUM RATINGS

Operating Temperature Industrial IM6102 ..... -40°C to +85°C Storage Temperature -65° C to 150° C Operating Voltage +4.0V to +7.0V Supply Voltage ..... +8.0V Voltage On Any Input or Output Pin ..... -0.3V to Vcc +0.3V NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

# D.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC} = 5.0V \pm 10\%$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$

|     |        |                              | CONDITIONS              | MIN          | TYP                | MAX  | UNITS       |

|-----|--------|------------------------------|-------------------------|--------------|--------------------|------|-------------|

| ٠ ١ | SYMBOL | PARAMETER                    |                         | Vcc-2.0      |                    |      | l v         |

| 1   | ViH    | Input Voltage High           |                         | VCC 2.0      | <del>  +</del>     | 0.8  | V           |

| 2   | VIL    | Input Voltage Low            |                         |              |                    | 1.0  | μА          |

| 3   | lin.   | Input Leakage 1              | GND≤Vin≤Vcc             | -1.0         | <del></del>        |      | V           |

| 4   | Voн    | Output Voltage High 2        | 10H = -0.2mA            | 2.4          |                    |      | <del></del> |

|     |        | Output Voltage Low           | I <sub>OL</sub> = 2.0mA |              |                    | 0.45 | V           |

| 5_  | VOL    |                              | GND≤Vouт≤Vcc            | -1.0         |                    | 1.0  | μΑ          |

| 6   | IOLK   | Output Leakage               | VIN=GND or Vcc          |              | 1.0                | 800  | μA          |

| 7   | Icc    | Power Supply Current-Standby |                         | <del> </del> | <del>  -:</del> -+ | 1.8  | mA          |

| 8   | Icc    | Power Supply Current-Dynamic | $f_C = 2.5MHz$          | <u> </u>     | 7.0                | 8.0  | pF          |

| 9   | Cin    | Input Capacitance 1          |                         |              |                    |      |             |

| 10  | Co     | Output Capacitance 1         |                         | <u> </u>     | 8.0                | 10.0 | pF          |

NOTE: 1. Except pins 15, 29, 31 2. Except pins 32, 33, 34.

# A.C. CHARACTERISTICS

TEST CONDITIONS: 5.0V  $\pm$  10%, C<sub>L</sub> = 50pF, T<sub>A</sub> = -40°C to +85°C, f<sub>C</sub> = 2.5MHz

| ٦,            | SYMBOL            | PARAMETER                                                         | MIN                                              | TYP                                              | MAX   | UNITS                                            |

|---------------|-------------------|-------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|-------|--------------------------------------------------|

|               |                   | LXMAR Pulse Width IN                                              | 300                                              |                                                  |       | ns                                               |

|               | tiin              | Address Setup Time IN: DX-LXMAR (1)                               | 80                                               |                                                  |       | ns                                               |

|               | tais              | Address Hold Time IN: LXMAR(I)-DX                                 | 120                                              |                                                  |       | ns                                               |

| $\rightarrow$ | taih              | Data Output Enable Time: DEVSEL(1)-DX                             | 1.20                                             | <u> </u>                                         | 400   | ns                                               |

|               | t <sub>den</sub>  | Controls Output Enable Time: DEVSEL(1)-lines C0,C1,C2,S/I         | <del>                                     </del> |                                                  | 400   | ns                                               |

|               | t <sub>cen</sub>  | Controls Output Enable Time. DEVSEC(1)-Inites 30,01,02,07.        | 100                                              | <del> </del>                                     |       | ns                                               |

| 6             | <sup>t</sup> dis  | Data Input Setup Time: DX-DEVSEL(1)                               | 100                                              | <del>                                     </del> |       | ns                                               |

| 7             | t <sub>dih</sub>  | Data Input Hold Time: DEVSEL(t)-DX                                | 500                                              | <del>                                     </del> |       | ns                                               |

| 8             | t <sub>rst</sub>  | RESET Input Pulse Width                                           | 300                                              | +                                                | 150   | ns                                               |

| 9             | t <sub>sid</sub>  | SKP/INTX to SKP/INT Propagation Delay                             |                                                  | <del> </del>                                     | - 100 | <del>                                     </del> |

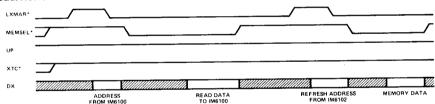

| 10            | <sup>t</sup> dmlx | DMA Control Signals Delay: XTC-XTC*; MEMSEL-MEMSEL*, LXMAR-LXMAR* |                                                  |                                                  | 150   | ns                                               |

| 11            | t <sub>dem</sub>  | Enable/Disable Time from DMAGNT to EMA Lines                      |                                                  |                                                  | 100   | ns                                               |

| 12            | t <sub>mdr</sub>  | MEMSEL* Pulse Width READ                                          | 750                                              |                                                  |       | ns                                               |

|               | t <sub>mdw</sub>  | MEMSEL* Pulse Width WRITE                                         | 950                                              |                                                  |       | ns                                               |

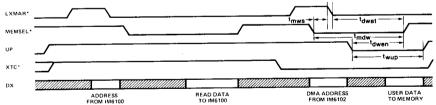

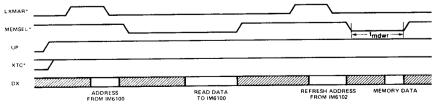

| 14            | tmdwr             | MEMSEL* Pulse Width WRITE/REFSH                                   | 550                                              |                                                  |       | ns                                               |

| 15            | tid               | LXMAR* Pulse Width                                                | 350                                              |                                                  |       | ns                                               |

| 16            | t <sub>drat</sub> | DMA READ Access Time: LXMAR*(1)-UP(1)                             | 750                                              |                                                  |       | ns                                               |

| 17            |                   | DX & EMA Address Setup Time Wrt LXMAR*(1)                         | 120                                              |                                                  |       | ns                                               |

| 18            | t <sub>dxas</sub> | DX & EMA Address Hold Time Wrt LXMAR*(1)                          | 175                                              |                                                  |       | ns                                               |

| 19            | t <sub>dxah</sub> | DMA READ Enable Time: MEMSEL* (1)-UP(t)                           | 550                                              |                                                  |       | ns                                               |

| 20            | t <sub>rup</sub>  | UP Pulse Width DMA READ                                           | 350                                              |                                                  |       | ns                                               |

|               |                   | DMA WRITE Access Time: LXMAR*(1)-MEMSEL*(1)                       | 750                                              |                                                  |       | ns                                               |

| 21            | tdwat             | DMA WRITE Enable Time: UP (1)-MEMSEL*(1)                          | 550                                              |                                                  |       | ns                                               |

| 22            | tdwen             | MEMSEL* Setup Time DMA WRITE MEMSEL*(1)-LXMAR*(1)                 | 100                                              |                                                  |       | ns                                               |

| 23            | t <sub>mws</sub>  | DMAEN Setup Time Wrt XTA (1)                                      | 100                                              |                                                  |       | ns                                               |

| 24            | t <sub>dms</sub>  | DMAEN Hold Time Wrt XTA (1)                                       | 100                                              | $\top$                                           |       | ns                                               |

| 25            | t <sub>dmh</sub>  |                                                                   | 750                                              |                                                  | T     | ns                                               |

| 26            | twup              | UP Pulse Width DMA WRITE                                          | / / 30                                           |                                                  |       |                                                  |

# IM6102A

### **ABSOLUTE MAXIMUM RATINGS**

Operating Temperature

Industrial IM6102A -40°C to +85°C

Storage Temperature -65°C to 150°C

Operating Voltage +4.0V to +11.0V

Supply Voltage +12.0V

Voltage On Any Input or

Output Pin -0.3V to Vcc +0.3V

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

# D.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC} = 10V \pm 5\%$ ,  $T_A = -40$ °C to +85°C

|    | SYMBOL | PARAMETER                    | CONDITIONS               | MIN      | TYP | MAX      | UNITS |

|----|--------|------------------------------|--------------------------|----------|-----|----------|-------|

| 1  | ViH    | Input Voltage High           |                          | 70% Vcc  |     |          | ٧     |

| 2  | VIL    | Input Voltage Low            |                          |          |     | 20% Vcc  | ٧     |

| 3  | In.    | Input Leakage(1)             | GND≤Vin≤Vcc              | -1.0     |     | 1.0      | μА    |

| 4  | Voн    | Output Voltage High(2)       | I <sub>OH</sub> = 0mA    | Vcc-0.01 |     |          | V     |

| -5 | Vol    | Output Voltage Low           | I <sub>OL</sub> = 0mA    |          |     | GND+0.01 | ٧     |

| 6  | lolk   | Output Leakage               | GND≤Vouт≤Vcc             | -1.0     |     | 1.0      | μΑ    |

| 7  | Icc    | Power Supply Current-Standby | Vin=GND or Vcc           |          |     | 900      | μΑ    |

| 8  | Icc    | Power Supply Current-Dynamic | f <sub>C</sub> = 5.71MHz |          |     | 4.0      | mA    |

| 9  | Cin    | Input Capacitance[1]         |                          |          | 7.0 | 8.0      | pF    |

| 10 | Co     | Output Capacitance[1]        |                          |          | 8.0 | 10.0     | pF    |

NOTE: 1. Except pins 15, 29, 31 2. Except pins 32, 33, 34.

### A.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC}$  = 10V  $\pm$  5%,  $C_L$  = 50pF,  $T_A$  = -40°C to +85°C,  $f_C$  = 5.71MHz

|    | SYMBOL            | PARAMETER                                                         | MIN | TYP      | MAX | UNITS |  |

|----|-------------------|-------------------------------------------------------------------|-----|----------|-----|-------|--|

| 1  | tiin              | LXMAR Pulse Width IN                                              | 125 |          |     | ns    |  |

| 2  | tals              | Address Setup Time IN: DX-LXMAR (1)                               | 50  |          |     |       |  |

| 3  | t <sub>alh</sub>  | Address Hold Time IN: LXMAR(4)-DX                                 | 50  |          |     | ns    |  |

| 4  | t <sub>den</sub>  | Data Output Enable Time: DEVSEL(I)-DX                             |     |          | 240 | ns    |  |

| 5  | t <sub>cen</sub>  | Controls Output Enable Time: DEVSEL(1)-lines C0,C1,C2,S/I         |     |          | 240 | ns    |  |

| 6  | t <sub>dis</sub>  | Data Input Setup Time: DX-DEVSEL(1)                               | 50  |          |     | ns    |  |

| 7  | t <sub>dih</sub>  | Data Input Hold Time: DEVSEL(1)-DX                                | 50  |          |     | ns    |  |

| 8  | t <sub>rst</sub>  | RESET Input Pulse Width                                           | 250 | <u>l</u> |     | ns    |  |

| 9  | t <sub>sid</sub>  | SKP/INTX to SKP/INT Propagation Delay                             |     |          | 100 | · ns  |  |

| 10 | t <sub>dmlx</sub> | DMA Control Signals Delay: XTC-XTC*; MEMSEL-MEMSEL*, LXMAR-LXMAR* |     | 100      |     | ns    |  |

| 11 | t <sub>dem</sub>  | Enable/Disable Time from DMAGNT to EMA Lines                      |     | 50       |     | ns    |  |

| 12 | t <sub>mdr</sub>  | MEMSEL* Pulse Width READ                                          | 300 |          |     |       |  |

| 13 | t <sub>mdw</sub>  | MEMSEL* Pulse Width WRITE                                         | 380 |          |     |       |  |

| 14 | <sup>t</sup> mdwr | MEMSEL* Pulse Width WRITE/REFSH                                   | 240 |          |     | ns    |  |

| 15 | t <sub>id</sub>   | LXMAR* Pulse Width                                                | 150 |          |     | ns    |  |

| 16 | t <sub>drat</sub> | DMA READ Access Time: LXMAR*(1)-UP(1)                             | 300 |          |     | ns    |  |

| 17 | t <sub>dxas</sub> | DX & EMA Address Setup Time Wrt LXMAR*(1)                         | 150 |          |     | ns    |  |

| 18 | tdxah             | DX & EMA Address Hold Time Wrt LXMAR*(1)                          | 55  |          |     | ns    |  |

| 19 | tdren             | DMA READ Enable Time: MEMSEL* (1)-UP(1)                           | 210 |          |     | ns    |  |

| 20 | t <sub>rup</sub>  | UP Pulse Width DMA READ                                           | 150 |          |     | ns    |  |

| 21 | tdwat             | DMA WRITE Access Time: LXMAR*(I)-MEMSEL*(1)                       | 300 |          |     | ns    |  |

| 22 | t <sub>dwen</sub> | DMA WRITE Enable Time: UP (4)-MEMSEL*(1)                          | 210 |          |     | ns    |  |

| 23 | t <sub>mws</sub>  | MEMSEL* Setup Time DMA WRITE MEMSEL*(1)-LXMAR*(1)                 | 50  |          |     | ns    |  |

| 24 | tdms              | DMAEN Setup Time Wrt XTA (1)                                      | 50  | \coprod  |     | ns    |  |

| 25 | tdmh              | DMAEN Hold Time Wrt XTA (1)                                       | 50  |          |     | ns    |  |

| 26 | twup              | UP Pulse Width DMA WRITE                                          | 300 |          | ns  |       |  |

# IM6102AM (Military)

# ABSOLUTE MAXIMUM RATINGS

Operating Temperature

Military IM6102AM .-55° C to +125° C

Storage Temperature .-65° C to 150° C

Operating Voltage .+4.0V to +11.0V

Supply Voltage .+12.0V

Voltage On Any Input or

Output Pin .-0.3V to Vcc +0.3V

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

# D.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC} = 10V \pm 5\%$ ,  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$

|                |        | DARAMETER                    | CONDITIONS     | MIN          | TYP     | MAX      | UNITS    |

|----------------|--------|------------------------------|----------------|--------------|---------|----------|----------|

|                | SYMBOL | PARAMETER                    |                | 70% Vcc      |         |          | V        |

| 1              | VIH    | Input Voltage High           |                | 7070100      |         | 20% Vcc  | V        |

| <del>5  </del> | VIL    | Input Voltage Low            |                |              |         |          | <u>-</u> |

| -              |        | Input Leakage[1]             | GND≤Vin≤Vcc    | -1.0         |         | 1.0      | μΑ       |

| 3              | lic.   |                              | IOH = 0mA      | Vcc-0.01     |         |          | V        |

| 4              | Vон    | Output Voltage High 2        | IOL = 0mA      |              |         | GND+0.01 | V        |

| 5              | Vol    | Output Voltage Low           |                | -1.0         |         | 1.0      | μА       |

| 6              | IOLK   | Output Leakage               | GND≤Vouт≤Vcc   | -1.0         |         |          |          |

| <del>,</del>   | Icc    | Power Supply Current-Standby | VIN=GND or Vcc |              | <u></u> | 900      | μA       |

|                |        | Power Supply Current-Dynamic | fc = 5.0MHz    |              | 1       | 4.0      | mA       |

| 8              | lcc    |                              |                | 1            | 7.0     | 8.0      | pF       |

| 9              | Cin    | Input Capacitance 1          |                | <del> </del> | 8.0     | 10.0     | pF       |

| 10             | Co     | Output Capacitance 1         |                | L            | 0.0     | 10.0     | <u> </u> |

NOTE: 1. Except pins 15, 29, 31 2. Except pins 32, 33, 34.

# A.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC}=10V\pm5\%,~C_L=50 pF,~T_A=-55^{\circ}C~to~+125^{\circ}C,~f_C=5.0 MHz$

| 1 t <sub>1</sub> 2 t <sub>2</sub> 3 t <sub>3</sub> 4 t t 5 t t 6 t t 7 t t 8 1 | tiin tais taih tcen tdis tdis tcen tdis tdih                             | PARAMETER  LXMAR Pulse Width IN  Address Setup Time IN: DX-LXMAR (1)  Address Hold Time IN: LXMAR(1)-DX  Data Output Enable Time: DEVSEL(1)-DX  Controls Output Enable Time: DEVSEL(1)-lines C0,C1,C2,S/I  Data Input Setup Time: DX-DEVSEL(1)  Data Input Hold Time: DEVSEL(1)-DX | 135<br>60<br>60<br>60 |              | 260<br>260 | ns<br>ns<br>ns<br>ns |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|------------|----------------------|

| 2 t, 3 t, 4 t t 5 t 6 t 7 t 8 1 9 1                                            | tais taih taih tden tcen tdis tdis tdih trst                             | Address Setup Time IN: DX-LXMAR (4) Address Hold Time IN: LXMAR(1)-DX Data Output Enable Time: DEVSEL(1)-DX Controls Output Enable Time: DEVSEL(4)-lines C0,C1,C2,S/I Data Input Setup Time: DX-DEVSEL(1) Data Input Hold Time: DEVSEL(1)-DX                                       | 60                    |              |            | ns                   |

| 3 t 4 t 5 t 6 t 7 t 8 t 9 t                                                    | taih tden tcen tdis tdis trst                                            | Address Hold Time IN: LXMAR(1)-DX  Data Output Enable Time: DEVSEL(1)-DX  Controls Output Enable Time: DEVSEL(1)-lines C0,C1,C2,S/I  Data Input Setup Time: DX-DEVSEL(1)  Data Input Hold Time: DEVSEL(1)-DX                                                                       | 60                    |              |            | ns                   |

| 4 t 5 t 6 t 7 t 8 t 9 t                                                        | t <sub>den</sub> t <sub>cen</sub> tdis t <sub>dih</sub> t <sub>rst</sub> | Data Output Enable Time: DEVSEL(1)-DX  Controls Output Enable Time: DEVSEL(1)-lines C0,C1,C2,S/I  Data Input Setup Time: DX-DEVSEL(1)  Data Input Hold Time: DEVSEL(1)-DX                                                                                                          |                       |              |            | +                    |

| 5 t 6 t 7 t 8 1 9 1                                                            | t <sub>cen</sub> tdis t <sub>dih</sub> t <sub>rst</sub>                  | Controls Output Enable Time: DEVSEL(1)-lines C0,C1,C2,S/I  Data Input Setup Time: DX-DEVSEL(1)  Data Input Hold Time: DEVSEL(1)-DX                                                                                                                                                 |                       |              | 260        | ns                   |

| 6 t 7 t 8 t 9 1                                                                | t <sub>dis</sub>                                                         | Data Input Setup Time: DX-DEVSEL(1)  Data Input Hold Time: DEVSEL(1)-DX                                                                                                                                                                                                            |                       | <del> </del> |            |                      |

| 7 t 8 t 9 1                                                                    | t <sub>dih</sub>                                                         | Data Input Hold Time: DEVSEL(1)-DX                                                                                                                                                                                                                                                 | 60                    |              | I          | ns                   |

| 8 1<br>9 1                                                                     | t <sub>rst</sub>                                                         |                                                                                                                                                                                                                                                                                    |                       |              |            | ns                   |

| 9 1                                                                            |                                                                          |                                                                                                                                                                                                                                                                                    | 250                   |              |            | ns                   |

|                                                                                | •                                                                        | RESET Input Pulse Width                                                                                                                                                                                                                                                            |                       | -            | 120        | ns                   |

| 10                                                                             | tsid                                                                     | SKP/INTX to SKP/INT Propagation Delay                                                                                                                                                                                                                                              | ļ                     | <del> </del> | 120        | +                    |

| 10   1                                                                         | t <sub>dmlx</sub>                                                        | DMA Control Signals Delay: XTC-XTC*; MEMSEL-MEMSEL*, LXMAR-LXMAR*  120                                                                                                                                                                                                             |                       |              | ns         |                      |

| 11 1                                                                           | t <sub>dem</sub>                                                         | Enable/Disable Time from DMAGNT to EMA Lines                                                                                                                                                                                                                                       |                       |              | 60         |                      |

|                                                                                | t <sub>mdr</sub>                                                         | MEMSEL* Pulse Width READ 375                                                                                                                                                                                                                                                       |                       |              | ns         |                      |

|                                                                                | t <sub>mdw</sub>                                                         | MEMSEL* Pulse Width WRITE                                                                                                                                                                                                                                                          | 475                   | 475          |            | ns                   |

|                                                                                | tmdwr                                                                    | MEMSEL* Pulse Width WRITE/REFSH                                                                                                                                                                                                                                                    | 275                   | ļ            |            | ns                   |

|                                                                                | tid                                                                      | LXMAR* Pulse Width                                                                                                                                                                                                                                                                 | 175                   |              |            | ns                   |

|                                                                                | t <sub>drat</sub>                                                        | DMA READ Access Time: LXMAR*(+)-UP(+)                                                                                                                                                                                                                                              | 375                   |              |            | ns                   |

|                                                                                | tdxas                                                                    | DX & EMA Address Setup Time Wrt LXMAR*(1)                                                                                                                                                                                                                                          | 70                    | L            |            | ns                   |

|                                                                                | t <sub>dxah</sub>                                                        | DX & EMA Address Hold Time Wrt LXMAR*(1)                                                                                                                                                                                                                                           | 70                    |              |            | ns                   |

|                                                                                |                                                                          | DMA READ Enable Time: MEMSEL* (I)-UP(I)                                                                                                                                                                                                                                            | 275                   |              |            | ns                   |

|                                                                                | t <sub>dren</sub>                                                        | UP Pulse Width DMA READ                                                                                                                                                                                                                                                            | 175                   |              |            | пѕ                   |

|                                                                                |                                                                          | DMA WRITE Access Time: LXMAR*(4)-MEMSEL*(1)                                                                                                                                                                                                                                        | 375                   |              | <u> </u>   | ns                   |

|                                                                                | t <sub>dwat</sub>                                                        | DMA WRITE Enable Time: UP (I)-MEMSEL*(I)                                                                                                                                                                                                                                           | 275                   |              |            | ns                   |

|                                                                                | t <sub>dwen</sub>                                                        | MEMSEL* Setup Time DMA WRITE MEMSEL*(1)-LXMAR*(1)                                                                                                                                                                                                                                  | 50                    |              |            | ns                   |

|                                                                                | t <sub>mws</sub>                                                         | DMAEN Setup Time Wrt XTA (1)                                                                                                                                                                                                                                                       | 50                    |              |            | ns                   |

|                                                                                | tdms                                                                     | DMAEN Hold Time Wrt XTA (1)                                                                                                                                                                                                                                                        | 50                    |              |            | ns                   |

| 25                                                                             | t <sub>dmh</sub>                                                         | UP Pulse Width DMA WRITE                                                                                                                                                                                                                                                           | 375                   |              | 1          | ns                   |

### IM6102-1

# **ABSOLUTE MAXIMUM RATINGS**

Operating Temperature

Industrial IM6102-11 -40°C to +85°C

Storage Temperature -65°C to 150°C

Operating Voltage +4.0V to +7.0V

Supply Voltage +8.0V

Voltage On Any Input or

Output Pin -0.3V to Vcc +0.3V

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

### D.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC} = 5.0V \pm 10\%$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$

|    | SYMBOL      | PARAMETER                    | CONDITIONS               | MIN                                              | TYP | MAX      | UNITS |

|----|-------------|------------------------------|--------------------------|--------------------------------------------------|-----|----------|-------|

| _  | <del></del> | Input Voltage High           |                          | V <sub>CC</sub> -2.0                             |     |          | V     |

| 1  | ViH         |                              |                          | <del>                                     </del> |     | 20% Vcc  | V     |

| 2  | VIL         | Input Voltage Low            | 0115-14                  | -1.0                                             |     | 1.0      | μΑ    |

| 3  | lic         | Input Leakage 11             | GND≤Vin≤Vcc              |                                                  | l   | 1.0      | - H   |

| 4  | VoH         | Output Voltage High 2        | I <sub>OH</sub> = -0.2mA | Vcc-0.01                                         |     |          |       |

| 5  | VOL         | Output Voltage Low           | I <sub>OL</sub> = 2.0mA  |                                                  |     | GND+0.01 | V     |

| 6  | lolk        | Output Leakage               | GND≤Vouт≤Vcc             | -1.0                                             |     | 1.0      | μΑ    |

| 7  | Icc         | Power Supply Current-Standby | VIN=GND or Vcc           |                                                  |     | 800      | μA    |

| 8  | lcc         | Power Supply Current-Dynamic | f <sub>C</sub> = 3.33MHz |                                                  |     | 2.0      | mA    |

| 9  | CIN         | Input Capacitance 1:         |                          |                                                  | 7.0 | 8.0      | pF    |

| 10 | Co          | Output Capacitance 1         |                          |                                                  | 8.0 | 10.0     | pF    |

NOTE: 1. Except pins 15, 29, 31 2. Except pins 32, 33, 34.

# A.C. CHARACTERISTICS

TEST CONDITIONS:  $5.0V \pm 10\%$ ,  $C_L = 50pF$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $f_C = 3.33MHz$

|    | SYMBOL            | PARAMETER                                                         | MIN | TYP | MAX        | UNITS |

|----|-------------------|-------------------------------------------------------------------|-----|-----|------------|-------|

| 1  | tiin              | LXMAR Pulse Width IN                                              | 250 |     |            | ns    |

| 2  | tais              | Address Setup Time IN: DX-LXMAR (4)                               | 70  |     |            | ns    |

| 3  | t <sub>aih</sub>  | Address Hold Time IN: LXMAR(1)-DX                                 |     |     |            | ns    |

| 4  | t <sub>den</sub>  | Data Output Enable Time: DEVSEL(1)-DX                             |     |     | 350        | ns    |

| 5  | t <sub>cen</sub>  | Controls Output Enable Time: DEVSEL(4)-lines C0,C1,C2,S/I         |     |     | 350        | ns    |

| 6  | tdis              | Data Input Setup Time: DX-DEVSEL 1                                | 100 |     |            | ns    |

| 7  | t <sub>dih</sub>  | Data Input Hold Time: DEVSEL 1:-DX                                | 100 |     |            | ns    |

| 8  | t <sub>rst</sub>  | RESET Input Pulse Width                                           | 500 |     |            | ns    |

| 9  | t <sub>sid</sub>  | SKP/INTX to SKP/INT Propagation Delay                             |     |     | 120        | ns    |

| 10 | t <sub>dmlx</sub> | DMA Control Signals Delay: XTC-XTC*; MEMSEL-MEMSEL*, LXMAR-LXMAR* |     | 120 |            | ns    |

| 11 | t <sub>dem</sub>  | Enable/Disable Time from DMAGNT to EMA Lines                      |     | 80  |            | ns    |

| 12 | t <sub>mdr</sub>  | MEMSEL* Pulse Width READ                                          | 550 |     |            | ns    |

| 13 | tmdw              | MEMSEL* Pulse Width WRITE                                         | 700 |     |            |       |

| 14 | t <sub>mdwr</sub> | MEMSEL* Pulse Width WRITE/REFSH                                   | 400 |     |            | ns    |

| 15 | tid               | LXMAR* Pulse Width                                                | 260 | ļ   |            | ns    |

| 16 | t <sub>drat</sub> | DMA READ Access Time: LXMAR* 1 -UP:1                              | 85  |     |            | ns    |

| 17 | tdxas             | DX & EMA Address Setup Time Wrt LXMAR* L                          | 125 |     | <u> </u>   | ns    |

| 18 | t <sub>dxah</sub> | DX & EMA Address Hold Time Wrt LXMAR* 1                           | 125 |     |            | ns    |

| 19 | t <sub>dren</sub> | DMA READ Enable Time: MEMSEL* 11-UPct                             | 400 |     |            | ns    |

| 20 | trup              | UP Pulse Width DMA READ                                           | 260 |     |            | ns    |

| 21 | tdwat             | DMA WRITE Access Time: LXMAR*(1)-MEMSEL*(1)                       | 550 |     |            | ns    |

| 22 | tdwen             | DMA WRITE Enable Time: UP : 1 - MEMSEL* 1:                        | 400 |     | L          | ns    |

| 23 | t <sub>mws</sub>  | MEMSEL* Setup Time DMA WRITE MEMSEL*(1)-LXMAR*(1)                 | 100 |     |            | ns    |

| 24 | t <sub>dms</sub>  | DMAEN Setup Time Wrt XTA                                          | 100 |     | ļ <u>.</u> | ns    |

| 25 | t <sub>dmh</sub>  | DMAEN Hold Time Wrt XTA                                           | 100 |     |            | ns    |

| 26 | twup              | UP Pulse Width DMA WRITE                                          | 550 |     | 1          | ns    |

# IM6102-1M (Military)

### **ABSOLUTE MAXIMUM RATINGS**

Operating Temperature

Military IM6102-1M -55°C to +125°C

Storage Temperature -65°C to 150°C

Operating Voltage +4.0V to +7.0V

Supply Voltage +8.0V

Voltage On Any Input or

Output Pin -0.3V to Vcc +0.3V

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

### D.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC} = 5.0V \pm 10\%$ ,  $C_L = 50pF$ ,  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$

|    | SYMBOL | PARAMETER                    | CONDITIONS              | MIN      | TYP | MAX  | UNITS |

|----|--------|------------------------------|-------------------------|----------|-----|------|-------|

| 1  | ViH    | Input Voltage High           |                         | Vcc -2.0 |     |      | V     |

| 2  | VIL    | Input Voltage Low            |                         |          |     | 0.8  | V     |

|    | lı.    | Input Leakage[1]             | GND≤Vin≤Vcc             | -1.0     |     | 1.0  | μА    |

| 4  | Vон    | Output Voltage High[2]       | I <sub>OH</sub> = 0mA   | 2.4      |     |      | V     |

| 5  | Vol    | Output Voltage Low           | I <sub>OL</sub> = 0mA   |          |     | 0.45 | v     |

| 6  | lork   | Output Leakage               | GND≤Vout≤Vcc            | -1.0     |     | 1.0  | μА    |

| 7  | Icc    | Power Supply Current-Standby | VIN=GND or VCC          |          |     | 800  | μΑ    |

| 8  | Icc    | Power Supply Current-Dynamic | f <sub>C</sub> = 2.5MHz |          |     | 2.0  | mA    |

| 9  | Cin    | Input Capacitance[1]         |                         |          | 7.0 | 8.0  | pF    |

| 10 | Co     | Output Capacitance[1]        |                         |          | 8.0 | 10.0 | pF    |

NOTE: 1. Except pins 15, 29, 31 2. Except pins 32, 33, 34.

# A.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC} = 5.0V \pm 10\%$ ,  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$ ,  $f_C = 2.5MHz$

|    | SYMBOL            | PARAMETER                                                              | MIN                            | TYP | MAX | UNITS |

|----|-------------------|------------------------------------------------------------------------|--------------------------------|-----|-----|-------|

| 1  | t <sub>lin</sub>  | LXMAR Pulse Width IN                                                   | 300                            |     |     | ns    |

| 2  | tais              | Address Setup Time IN: DX-LXMAR (4)                                    | 80                             |     |     | ns    |

| 3  | taih              | Address Hold Time IN: LXMAR(4)-DX                                      | 120                            |     |     | ns    |

| 4  | t <sub>den</sub>  | Data Output Enable Time: DEVSEL(4)-DX                                  |                                |     | 400 | ns    |

| 5  | t <sub>cen</sub>  | Controls Output Enable Time: DEVSEL(4)-lines C0,C1,C2,S/I              |                                |     | 400 | ns    |

| 6  | tdis              | Data Input Setup Time: DX-DEVSEL:1                                     | 100                            |     |     | ns    |

| 7  | tdih              | Data Input Hold Time: DEVSEL 1 -DX                                     | 100                            |     |     | ns    |

| 8  | t <sub>rst</sub>  | RESET Input Pulse Width                                                | 500                            |     |     | ns    |

| 9  | t <sub>sid</sub>  | SKP/INTX to SKP/INT Propagation Delay                                  |                                |     | 130 | ns    |

| 10 | t <sub>dmlx</sub> | DMA Control Signals Delay: XTC-XTC*: MEMSEL-MEMSEL*, LXMAR-LXMAR*  130 |                                | ns  |     |       |

| 11 | t <sub>dem</sub>  | Enable/Disable Time from DMAGNT to EMA Lines                           | to EMA Lines 100               |     | ns  |       |

| 12 | t <sub>mdr</sub>  | MEMSEL* Pulse Width READ                                               | 750                            | 0   |     | ns    |

| 13 | tmdw              | MEMSEL* Pulse Width WRITE                                              | 950                            |     | ns  |       |

| 14 | t <sub>mdwr</sub> | MEMSEL* Pulse Width WRITE/REFSH                                        | L* Pulse Width WRITE/REFSH 550 |     |     | ns    |

| 15 | tid               | LXMAR* Pulse Width                                                     | 350                            |     |     | ns    |

| 16 | t <sub>drat</sub> | DMA READ Access Time: LXMAR*+1UP+1                                     | 750                            |     |     | ns    |

| 17 | t <sub>dxas</sub> | DX & EMA Address Setup Time Wrt LXMAR*11                               | 120                            |     |     | ns    |

| 18 | t <sub>dxah</sub> | DX & EMA Address Hold Time Wrt LXMAR* I                                | 175                            |     |     | ns    |

| 19 | t <sub>dren</sub> | DMA READ Enable Time: MEMSEL* (1)-UP(1)                                | 550                            |     |     | ns    |

| 20 | t <sub>rup</sub>  | UP Pulse Width DMA READ                                                | 350                            |     |     | ns    |

| 21 | t <sub>dwat</sub> | DMA WRITE Access Time: LXMAR*(4)-MEMSEL*(1)                            | 750                            |     |     | ns    |

| 22 | t <sub>dwen</sub> | DMA WRITE Enable Time: UP (I)-MEMSEL*(1)                               | 550                            |     |     | ns    |

| 23 | t <sub>mws</sub>  | MEMSEL* Setup Time DMA WRITE MEMSEL*:11-LXMAR*:11:                     | 100                            |     |     | ns    |

| 24 | t <sub>dms</sub>  | DMAEN Setup Time Wrt XTA -t-                                           | 100                            |     |     | ns    |

| 25 | t <sub>dmh</sub>  | DMAEN Hold Time Wrt XTA +1                                             | 100                            |     |     | ns    |

| 26 | twup              | UP Pulse Width DMA WRITE                                               | 750                            |     |     | ns    |

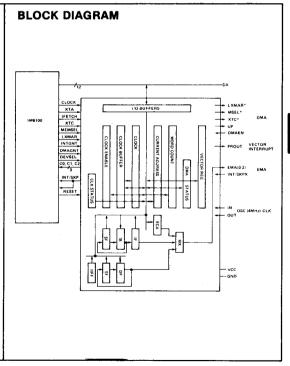

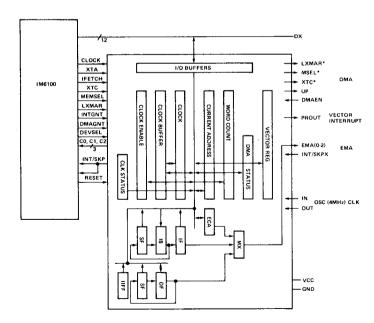

### **ARCHITECTURE**

The IM6102 is composed of three distinct functions:

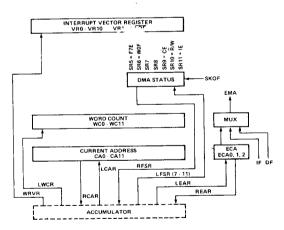

- a) A DMA port that uses the bus during the second half of a cycle to read, write, or refresh memory. The DMA port logic includes a word count register WC, a current address register CA, an extended current address register ECA, and a DMA status register.

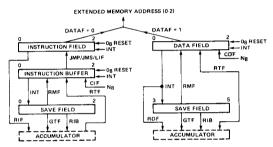

- b) An extended memory address controller that augments the 12-bit addresses generated by the IM6100 microprocessor by supplying a 3-bit address field that may be decoded to select one of eight 4096 word memory fields. The memory extension controller logic consists of an instruction field register IF, a data field register DF, an instruction buffer register IB, and a save field register SF.

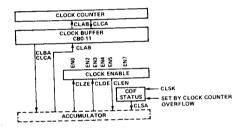

- c) A realtime clock whose mode and time base rate may be programmed by the user. The clock logic includes a clock enable register CE, a clock buffer register CB, a clock counter register CC, and a time base multiplexer.

A block diagram of the IM6102 is shown in Figure 1.

The IM6102 registers are summarized as follows:

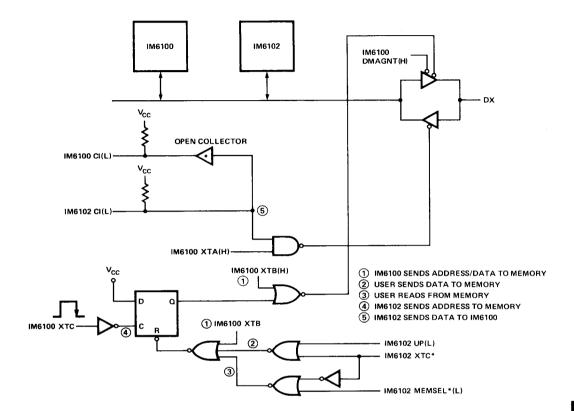

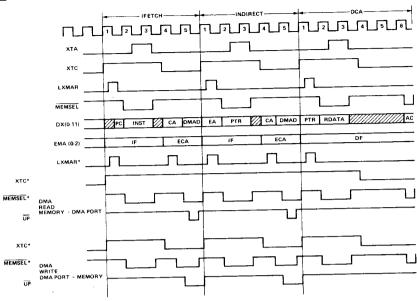

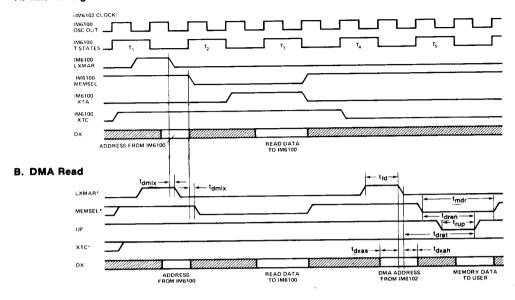

### A. Simultaneous DMA Channel (Figure 3)

### **CURRENT ADDRESS (CA) REGISTER**

This register is a 12-bit presettable binary counter. At the beginning of a SDMA transfer, the current address must be set to the first location to be accessed. The content of the CA register is incremented by 1 after a SDMA transfer, and the incremented value is used as the address of the memory location with which the next transfer will be performed.

### EXTENDED CURRENT ADDRESS (ECA) REGISTER

This is a 3-bit presettable binary counter and if the carry enable bit of the DMA status register is set, the 12-bit CA register and the 3 ECA bits are treated as one 15-bit register with the ECA bits most significant. If memory field 7 (all 3 bits at logic one) is selected, the ECA cannot increment, but will wrap around in field 7 and an F7 error (F7E) will occur. The Interrupt Enable bit IE in SR11must be set to enable F7E interrupts. If enabled the F7E will request an interrupt. If the carry enable bit CE in SR9 is not set, the ECA, is not incremented when CA goes from 77778 to 00008.

#### WORD COUNT (WC) REGISTER

A 12-bit presettable binary counter is used as a word counter. At the beginning of a SDMA transfer, the two's complement of the number of 12-bit words to be transferred must be loaded into the WC. If enabled this will initiate the SDMA operation. The WC register is incremented by 1 after a SDMA transfer. If this value becomes zero, word count overflow has occurred and if the IE bit in SR11 is set, interrupts are enabled and an interrupt is requested. Unless instructed to be in the continuous run mode, a WC overflow inhibits further transfers. The WOF is set when the MSB of the WC register makes a "1" to "0" transition.

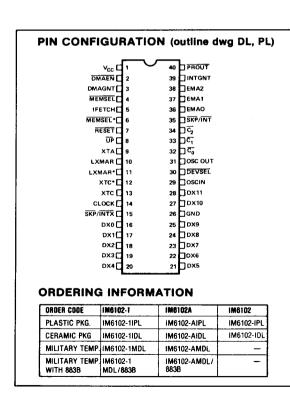

FIGURE 1: IM6102 MEMORY EXTENSION/DMA/INTERVAL TIMER CONTROLLER (MEDIC)

8-81

| 1  | \ <u></u>                                                                             | 40                                                                                         | PROUT                                                                                                      |

|----|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 2  |                                                                                       | 39                                                                                         | INTGNT                                                                                                     |

| 3  |                                                                                       | 38                                                                                         | □EMA2                                                                                                      |

| 4  |                                                                                       | 37                                                                                         | □EMA1                                                                                                      |

| 5  |                                                                                       | 36                                                                                         | ]EMAO                                                                                                      |

| 6  |                                                                                       | 35                                                                                         | SKP/INT                                                                                                    |

| 7  |                                                                                       | 34                                                                                         | ⊒ ব্                                                                                                       |

| 8  |                                                                                       | 33                                                                                         | ⊐द                                                                                                         |

| 9  |                                                                                       | 32                                                                                         | ⊅ଜ                                                                                                         |

| 10 |                                                                                       | 31                                                                                         | Dosc out                                                                                                   |

| 11 |                                                                                       | 30                                                                                         | DEVSEL                                                                                                     |

| 12 |                                                                                       | 29                                                                                         | OSCIN                                                                                                      |

| 13 |                                                                                       | 28                                                                                         | DX11                                                                                                       |

| 14 |                                                                                       | 27                                                                                         | DDX10                                                                                                      |

| 15 |                                                                                       | 26                                                                                         | □GND                                                                                                       |

| 16 |                                                                                       | 25                                                                                         | □охэ                                                                                                       |

| 17 |                                                                                       | 24                                                                                         | DX8                                                                                                        |

| 18 |                                                                                       | 23                                                                                         | □DX7                                                                                                       |

| 19 |                                                                                       | 22                                                                                         | DDX6                                                                                                       |

| 20 |                                                                                       | 21                                                                                         | DDX5                                                                                                       |

|    | 3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18 | 3<br>4<br>5<br>6<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18 | 2 39 39 3 38 4 37 5 5 36 6 35 7 34 8 33 9 32 10 31 11 30 12 29 13 28 8 14 27 15 26 16 25 17 24 18 23 19 22 |

# IM6102 FUNCTIONAL PIN DESCRIPTION

| Pin<br>Number | Symbol        | Input/<br>Output | Description                                                                                                                                                                                       |

|---------------|---------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | Vcc           |                  | Supply voltage                                                                                                                                                                                    |

| 2             | DMAEN         | l l              | Enable the IM6102 DMA chan-<br>nel to transfer data                                                                                                                                               |

| 3             | DMAGNT        | t                | Direct memory access grant from CPU                                                                                                                                                               |

| 4             | MEMSEL        | 1                | Memory select for read or write from CPU                                                                                                                                                          |

| 5             | IFETCH        | ١                | CPU flag indicating instruction fetch cycle                                                                                                                                                       |

| 6             | MEMSEL*       | 0                | Memory select generated by the IM6102                                                                                                                                                             |

| 7             | RESET         | l                | Asynchronous reset will clear Instruction Field to 0s, disable all interrupts, initialize DMA port to READ/REFRESH, initialize timer to "stop", "divide by 212 mode" and "enable divide counters" |

| 8             | <del>UP</del> | 0                | User pulse (read or write)                                                                                                                                                                        |

| 9             | XTA           | ı                | CPU external minor cycle tim-<br>ing signal                                                                                                                                                       |

| 10            | LXMAR         | 1                | A falling edge of LXMAR pulse<br>from CPU will load external<br>memory address register                                                                                                           |

| Pin<br>Number | Symbol         | Input/<br>Output                                                 | Description                                                               |  |

|---------------|----------------|------------------------------------------------------------------|---------------------------------------------------------------------------|--|

| 11            | LXMAR*         | 0                                                                | LXMAR generated by the IM6102                                             |  |

| 12            | хтс•           | 0                                                                | XTC generated by the IM6102                                               |  |

| 13            | хтс            | 1                                                                | CPU external minor cycle tim-<br>ing signal                               |  |

| 14            | CLOCK          | 1                                                                | Oscillator OUT pulses from CPU for timing the IM6102 DMA transfers.       |  |

| 15            | SKP/INTX       | 1                                                                | Multiplexed SKP/INT line from lower priority devices                      |  |

| 16            | DX0            | I/O Most significant bi<br>12-bit multiplexed ad<br>data I/O bus |                                                                           |  |

| 17            | DX1            | 1/0                                                              | See pin 16-DX0                                                            |  |

| 18            | DX2            | 1/0                                                              | See pin 16-DX0                                                            |  |

| 19            | DX3            | 1/0                                                              | See pin 16-DX0                                                            |  |

| 20            | DX4            | 1/0                                                              | See pin 16-DX0                                                            |  |

| 21            | DX5            | 1/0                                                              | See pin 16-DX0                                                            |  |

| 22            | DX6            | 1/0                                                              | See pin 16-DX0                                                            |  |

| 23            | DX7            | 1/0                                                              | See pin 16-DX0                                                            |  |

| 24            | DX8            | 1/0                                                              | See pin 16-DX0                                                            |  |

| 25            | DX9            | 1/0                                                              | See pin 16-DX0                                                            |  |

| 26            | GND            | 1/0                                                              | Power Supply                                                              |  |

| 27            | DX10           | 1/0                                                              | See pin 16-DX0                                                            |  |

| 28            | DX11           | 1/0                                                              | See pin 16-DX0                                                            |  |

| 29            | OSCIN          | 1                                                                | Crystal input for timer oscil-<br>lator                                   |  |

| 30            | DEVSEL         | 1                                                                | Device select for read or write from CPU                                  |  |

| 31            | OSC OUT        | 0                                                                | See pin 29                                                                |  |

| 32            | C <sub>0</sub> | 0                                                                | Control lines to CPU determin-<br>ing type of peripheral data<br>transfer |  |

| 33            | C <sub>1</sub> | 0                                                                | See pin 32-C <sub>0</sub>                                                 |  |

| 34            | <u>C</u> 2     | 0                                                                | See pin 32-C <sub>0</sub>                                                 |  |

| 35            | SKP/INT        | 0                                                                | Multiplexed SKP/INT input to the CPU                                      |  |

| 36            | EMAO           | 0                                                                | Extended memory address field (most significant bit)                      |  |

| 37            | EMA1           | 0                                                                | Extended memory address field                                             |  |

| 38            | EMA2           | 0                                                                | Extended memory address field                                             |  |

| 39            | INTGNT         | 1                                                                | CPU interrupt grant                                                       |  |

| 40            | PROUT          | 0                                                                | Priority out for vectored inter-<br>rupt                                  |  |

NOTE: All DX lines are bidirectional with three-state outputs: Pins 6, 8, 11, 12, 35, 40 have active pullups; pins 32, 33, 34 have open drain outputs; pin 15 has a resistive input pullup; all inputs are protected with resistors and clamp diodes.

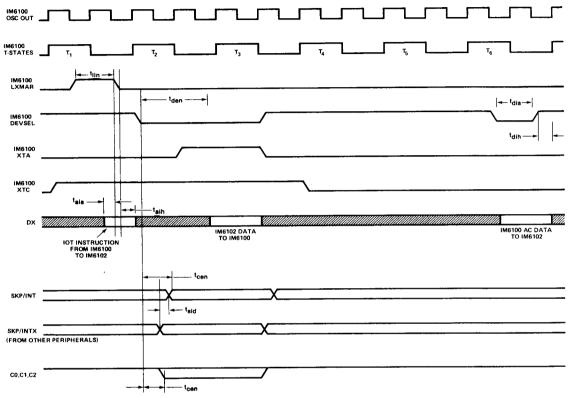

FIGURE 2: MEDIC TIMING FOR DCA I

# **DMA Status Register**

This register consists of 5 control bits and 2 flag bits for the SDMA feature. For a description refer to the register bit assignments.

FIGURE 3: SDMA REGISTERS

### **OPERATION**

The IM6102 SDMA channel augments the throughput of the IM6100 during DMA operations by transferring data between memory and peripheral devices simultaneously with

normal processor bus usage. In other words, no memory cycles are "stolen" from the processor; but the DMA address and data are transferred on the bus during periods that the DX bus is inactive.

8-83

Printed from www.freetradezone.com, a service of Partminer, Inc. This Material Copyrighted By Its Respective Manufacturer

### TABLE 1 SUMMARY OF IM6102 INSTRUCTIONS

|              | OCTAL  | 1/O C                                            | ONTROL LI          | NES      | OPERATION                                                                    |

|--------------|--------|--------------------------------------------------|--------------------|----------|------------------------------------------------------------------------------|

| MNEMONIC     | CODE   | C0                                               | C1                 | C2       |                                                                              |

| GTF          | 6004   | 0                                                | 0                  | 1        | ① Get flags, INT INH FF $\rightarrow$ AC(3), SF (0-5) $\rightarrow$ AC(6-11) |

| RTF          | 6005   | 1                                                | 1 +                | 1        | ② Return flags, AC(6-8) → IB, AC(9-11) → DF                                  |

| CDF          | 62N1   | <del>- i -  </del>                               | <del>i</del>       | 1        | Change Data Field, N → DF                                                    |

| CIF          | 62N2   | 1 1                                              | 1                  | 1        | Change IF, N → IB                                                            |

| CDF, CIF     | 62N3   | 1                                                | <del>- i -  </del> | 1        | Combination of CDF, CIF                                                      |

| RDF          | 6214   | 1                                                | <del>- i</del> -   | 1        | Read DF, DF + AC(6-8) → AC(6-8)                                              |

| RIF          | 6224   | 1                                                | 0                  | 1        | Read IF, IF + AC(6-8) →AC(6-8)                                               |

| RIB          | 6234   | 1                                                | 0                  | <u>i</u> | Read Save Field, SF + AC(6-11) → AC(6-11)                                    |

|              | 6244   | 1                                                | 1                  | 1        | Restore Mem. Field, SF(0·2) → IB, SF(3·5) → DF                               |

| RMF          | 6254   | 1                                                | <del>i</del>       | 1        | Load IF, IB → IF                                                             |

| LIF          | 0254   | '                                                | '                  | •        |                                                                              |

| CL 7E        | 6130   | 1                                                | 1                  | 1        | Clear Clock Enable Register if corresponding AC bit is set                   |

| CLZE         | 0130   | '                                                | · ·                |          | AC not changed                                                               |

| CI CI        | 6131   | 1                                                | 1                  | 1        | Skip on Clock Overflow Interrupt condition                                   |

| CLSK         | 6132   | 1                                                | 1                  | 1        | Set Clock Enable Register if corresponding AC bit is set                     |

| CLOE         | 6132   | ' 1                                              | '                  | ,        | AC not changed                                                               |

| 01.45        | 6133   | 1                                                | 1                  | 1        | AC → Clock Buffer; Clock Buffer → Clock Counter;                             |

| CLAB         | 0133   | •                                                | •                  |          | AC not changed                                                               |

| CLEN         | 6134   | 0                                                | 0                  | 1        | Clock Enable Register - AC                                                   |

| CLEN         | 6135   | 0                                                | 0                  | 1        | COF → AC(0), Clear COF Status bit                                            |

| CLSA         | 6136   | 0                                                | 0                  | 1        | Clock Buffer → AC                                                            |

| CLBA         | 6137   | 0                                                | 0                  | 1        | Clock Counter → Clock Buffer; Clock Buffer → AC                              |

| CLCA         | 6137   | "                                                |                    |          |                                                                              |

| 1000         | 6205   | 0                                                | 1                  | 1        | AC → Current Address Register, 0 → AC                                        |

| LCAR<br>RCAR | 6215   | 0                                                | 0                  | 1        | Current Address Register AC                                                  |

|              | 6225   | 0                                                | 1                  | 1        | AC → Word Count Register, Start DMA, 0 → AC; clears word                     |

| LWCR         | 6225   | 1                                                |                    |          | count overflow (WOF)                                                         |

| 1545         | 62N6   | 1                                                | 1                  | 1        | N → Extended Current Address Register (ECA)                                  |

| REAR         | 6235   | <del>                                     </del> | 0                  | 1        | Read ECA, ECA + AC(6-8) → AC(6-8)                                            |

| LFSR         | 6245   | 0                                                | 1                  | 1 1      | AC(7-11) → Status Register, 0 → AC                                           |

| RFSR         | 6255   | 1                                                | 0                  | 1        | DMA Status Register + AC(5-11) → AC(5-11); clears Field 7                    |

| KFSN         | 0255   | '                                                |                    |          | Wraparound error (F7E)                                                       |

| SKOF         | 6265   | 1                                                | 1                  | 1-1      | Skip on Word Count Overflow                                                  |

| WRVR         | 6275   | 0                                                | 1                  | 1        | AC(0·10) → Vector Register, 0 → AC                                           |

| I why        | 02/5   |                                                  |                    |          |                                                                              |

| CAF          | 6007   | 1                                                | 1                  | 1        | 3 Clear all flags (F7E, W0F, COF) Clear clock Enable                         |

| I CAF        | 1 0007 | 1 '                                              | ,                  | 1        | register, clock buffer                                                       |

- 1. The internal flags of the IM6100 are defined as follows: LINK → AC (Q), INTREQ → AC (2) and INTERRUPT ENABLE FF → AC (4).

- 2. When RTF is executed, the LINK is restored from AC (0) and the Interrupt System is enabled after the next sequential instruction is executed. The Interrupt Inhibit FF is set preventing interrupts until the next JMP, JMS or LIF instruction is executed.

- 3. A hardware RESET clears F7E, W0F, 11FF and COF. The IF and DF are cleared to O8. The DMA status register is cleared. (Read; refresh; disable F7E and W0F interrupts; no carry from CAO to ECA2). The clock Enable register is cleared (Disable COF interrupt; disable clock buffer to clock counter transfer on COF; disable counter). Counter/buffer is cleared.

# TABLE 2 SUMMARY OF IM6102 REGISTER BIT ASSIGNMENTS

|                          | DX0 | DX1 | DX2 | DX3      | DX4 | DX5 | DX6  | DX7  | DX8  | DX9 | DX10 | DX11 |

|--------------------------|-----|-----|-----|----------|-----|-----|------|------|------|-----|------|------|

| Current Address          | CA0 | CA1 | CA2 | CA3      | CA4 | CA5 | CA6  | CA7  | CA8  | CA9 | CA10 | CA11 |

| Extended Current Address |     |     |     |          |     |     | ECA0 | ECA1 | ECA2 |     |      |      |

| Word Count               | WCO | WC1 | WC2 | WC3      | WC4 | WC5 | WC6  | WC7  | WC8  | WC9 | WC10 | WC11 |

| DMA Status (1)           |     |     | 1   |          |     | SR5 | SR6  | SR7  | SR8  | SR9 | SR10 | SR11 |

| Interrupt Vector (2)     | VRO | VR1 | VR2 | VR3      | VR4 | VR5 | VR6  | VR7  | VR8  | VR9 | VR10 | VR11 |

| RIF Instruction (3)      |     |     |     | T        |     |     | IF0  | IF1  | IF2  |     |      |      |

| RTF, CIF Instruction     |     |     |     |          |     |     | 1B0  | IB1  | IB2  |     |      |      |

| GTF, RIB Instruction     |     |     |     | HFF(4)   |     |     | SF0  | SF1  | SF2  | SF3 | SF4  | SF5  |

| CDF, RDF Instruction     |     |     |     |          |     |     | DF0  | DF1  | DF2  |     |      |      |

| RTF Instruction          |     | 1   |     | <u> </u> |     |     |      |      |      | DF0 | DF1  | DF2  |

| Clock Enable (5)         | EN0 |     | EN2 | EN3      | EN4 | EN5 |      | EN7  |      |     |      |      |